Simulateurs

Rôle du simulateur

Le simulateur ne connait que des modèles VHDL c’est à dire des objets décrit dans la norme du langage vhdl. En aucun cas , ce simulateur n’est capable de dire si le modèle qui lui est soumis correspond ou non à un circuit (cela c’est le synthètiseur qui pourra le dire). La simulation est par nature comportementale.

Le simulateur contient un compilateur dont le rôle est de détecter les erreurs éventuelles de syntaxe ou certaines incohérences d’écriture et conjointement de transformer le source VHDL en un code exécutable qui lui est propre. Les objets produits sont tous de type logico temporels ( un retard nul est remplacé par un délai delta).

Pour tester un modèle , on doit lui appliquer des stimuli c’est à dire des générateurs sur les entrées. On peut aussi vouloir tester automatiquement les sorties et placer dans le test des points d’observation. Dans de nombreux cas, les stimuli vont dépendre des sorties obtenues ce qui pose un problème de « dynamique ». L’ensemble des stimuli sont les vecteurs de test appelés dans la littérature américaine testbench ou benchmark. Ce « testbench » va être significatif de la qualité du test qui peut d’ailleurs être quantifiée par le simulateur. Chaque simulateur peut offrir sa propre méthode de description des stimuli mais décrire l’ensemble du test avec ce même langage VHDL permet et de bénéficier de la puissance du langage, et de s’affranchir du compilateur et donc de disposer d’un test portable.

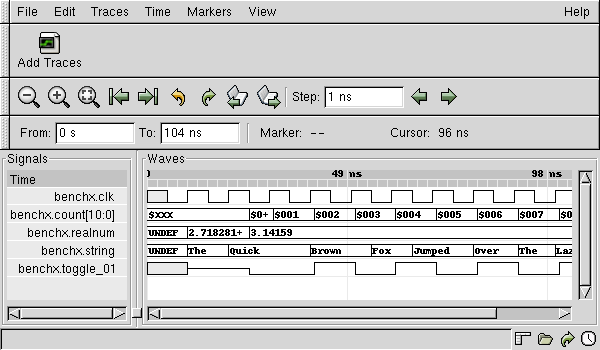

Le résultat de simulation après exécution se présente sous la forme d’une fonction du temps. Le simulateur doit disposer d’un module de présentation des résultats sous forme tabulaire ou de chronogrammes.

En résumé, le simulateur est un outil indispensable pour:

- Vérifier rapidement la syntaxe

- Etablir une stratégie de test

- s’assurer du bon comportement du circuit avant synthèse

- S’assurer que la fonctionnalité du circuit après synthèse est bien conforme

- Apprécier avec exactitude les problèmes engendrés par les retards sur le circuit « vrai » après placement/routage.

Quel simulateur ?

Depuis plus de 10 ans, ce simulateur proféssionnel a montré ses qualités et sa robustesse. Un grand nombre d’écoles l’ont diffusé, de plus , il a été adopté par de grands noms tels que Xilinx et Altera qui en proposent un version gratuite avec leur logiciel de placement/routage ( voir page implantation). La version professionnelle et disponible chez Mentor Graphics . Windows, Unix et Linux sont supportés. Modelsim est donc le simulateur à conseiller.

Depuis plus de 10 ans, ce simulateur proféssionnel a montré ses qualités et sa robustesse. Un grand nombre d’écoles l’ont diffusé, de plus , il a été adopté par de grands noms tels que Xilinx et Altera qui en proposent un version gratuite avec leur logiciel de placement/routage ( voir page implantation). La version professionnelle et disponible chez Mentor Graphics . Windows, Unix et Linux sont supportés. Modelsim est donc le simulateur à conseiller.

ISE Simulateur (ISIM)

Intégré à la suite logicielle Xilinx ISE, il est donc gratuit avec le webpack

On trouvera un excellent tutorial à l’adresse suivante:

GHDL

Pour les possesseurs de MAC OSX (et aussi Linux et windows ?), il existe un compilateur VHDL gratuit ghdl qui doit être associé au module de visualisation (gratuit) GTKWave pour constituer un simulateur VHDL complet.

Vous voilà prêts à vos premières simulation ….

REMARQUE : Pour le principe de fonctionnement par événement du simulateur, on se reportera aux explications disponibles dans le cours de P.Nouel: langage vhdl .

À propos de ghdl, l’avez-vous déjà utilisé ? Si oui l’avez vous déjà utilisé pour faire des simulations post placement routage ?

Je serais très intéressé d’avoir une explication de la compilation des librairies unisim et simprim pour faire de la simu post routage sur spartan (avec les outils du xilinx web pack), car on trouve très peu de documentation sur le sujet.

remarque : ise aussi peut faire de la simulation.

Oui , j’ai testé ghdl sur MAC mais pas de façon très poussée. Je n’ai pas fait de simulations post Routage . J’espère dans un avenir proche l’avoir fait car je vais développer la partie premier projet du site .

Sous modelsim c’est assez simple.

1- Il faut créer la bibliothèque unisim par la commande vlib unisim (unisim représente un répertoire qui sera créé)] [

]) le premier unisim est le nom logique de la bibliothèque , le second est le nom du répertoire précédent ( qui aurait pu s’appeler toto)

2- il faut installer cette bibliothèque (mapping) vmap unisim unisim (# Usage: vmap [-help] [-c] [-del] [

3- Il faut se procurer les sources VHDL par exemple dans

C:\Xilinx91i\vhdl\src\unisims

4-Il faut les compiler dabs la nouvelle bibliothèque: vcom -work unisim C:\Xilinx91i\vhdl\src\unisims\unisim_VPKG.vhd

5- même chose pour les autres fichiers

6- même chose pour simprim

7- ne pas oublier à l’utilisation de déclarer ces bibliothèques

P.S : Attention ! , l’ordre des fichiers est important (compiler d’abord

les packages )