Implantation

Le projet ne comporte que des sources VHDL qui se trouvent toutes dans le répertoire .\rtl. On associera au projet tous les fichiers exceptés new_pps_ppx.vhd (qui sera utilisé plus tard) et rom84_sim.vhd qui est le fichier qui remplace rom84.vhd lors des simulations. C’est l’entité pic qui doit se trouver au sommet du projet, il est conseillé de placer le fichier ppx_pack.vhd en tête des fichiers.

Implantation Altera

lLe fichier pic.vhd est au sommet du projet. Il faut ensuite assurer le mappings des entrées-sorties de la carte de développement. Un exemple par fichier TCL est fourni pour une carte Stratix Altera.

Implantation ise

Un exemple est donné d’implantation sur une carte de développement Spartan3 de xilinx. le plus simple est de rajouter une couche de description de la carte et de tenir comte des spécificités des entrées-sorties. Cela donne le fichier s3board.vhd qui viendra se placer au sommet du projet. On adjoindra aux sources du projet le fichier s3board.ucf de description de l’emplacement des entrées-sorties sur la carte.

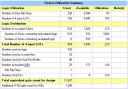

Voici le rapport résumé d’implantation:

Une fois l’implantation terminée, lorsqu’on configure la carte, que constate t-on ?

Le chenillard fonctionne mais il n’y a qu’une diode sur deux qui s’allume.

Voilà qui est intéressant. Il y a une erreur dans le modèle de PIC, il va falloir le corriger. pour cela , on va d’abord effectuer une simulation.

Leave a Reply

You must be logged in to post a comment.